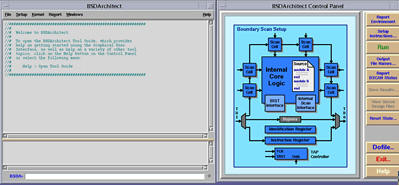

BSDArchitect在逻辑综合之前的RTL设计阶段自动生成边界扫描电路和IO管脚的自动插入。为实现自动验证,它还生成一个可用于任何VHDL或Verilog仿真器的测试基准文件;此外,BSDArchitect形成设计的BSDL模型,为生成ATPG测试向量做准备。为了实现更好的性能可预测性和设计复用,也可以直接插入实现在特定工艺上的边界扫描电路。在SOC测试中,BSDArchitect还利用IEEE 1149.1边界扫描结构中的自定义指令进行全片的测试管理。

主要特点:

BSDArchitect读入IC、ASIC或MCM设计的行为级VHDL或Verilog描述,生成符合IEEE1149.1边界扫描标准的VHDL或Verilog电路描述,并将它插入到原来的设计中;

支持实现IEEE 1149.1边界扫描结构中的自定义指令逻辑,实现对内部扫描和BIST的芯片级测试互连与测试过程控制,缩短IC实现周期;

可以实现直接插入针对特定工艺上的边界扫描电路;

支持IO管脚的自动插入,可以实现直接插入针对特定工艺的IO管脚;

自动生成边界扫描描述语言(BSDL)文件, 提供到自动测试设备(ATE)的平滑过渡;

自动生成Verilog或VHDL格式的测试基准向量进行边界扫描逻辑的功能检查,包括对BSDL的自适应检查;

支持UNIX平台(Solaris, HP-PA)。