| |

|

近期热点 |

|

|

|

相关文章 |

|

|

|

相关新闻 |

|

|

|

相关热贴 |

|

|

|

相关商城商品 |

|

|

|

| |

|

|

| 当前位置:技术信息化 -> EDA |

| |

| | Leda RTL Checker――可编程检查器 | | 发表时间:2006-9-30 | | 关键字:Leda RTL Checker 产品分析 | | | Synopsys 的LEDA是一种可编程代码设计规则检查器,它提供全芯片级混合语言(Verilog和VHDL)处理能力,从而加快了复杂的SOC设计的开发。 |

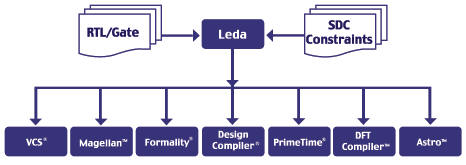

| | Synopsys 的LEDA是一种可编程代码设计规则检查器,它提供全芯片级混合语言(Verilog和VHDL)处理能力,从而加快了复杂的SOC设计的开发。LEDA预装的检查规则大大地增强了设计人员检查HDL代码的能力,包括可综合性,可仿真性、可测试性和可重用性。利用所提供的设计规则,能进一步的提高Synopsys工具,例如VCS、Design Compiler以及Formality的性能。LEDA的规则集有助于设计人员共享他们的设计经验,对硬件设计预检查,且将设计风险降到最低。 使用LEDA,可以对硬件设计的仿真和综合进行预检查,消除设计流程中的瓶颈,其中Verilog代码设计规则可确保按内部或外部工具要求优化代码 。LEDA提供的设计规则可提高Synopsys工具的性能。

● 支持Verilog/VHDL混合语言的设计

● 包含先进的硬件设计推测和层次化检查的能力,确保设计人员对特殊硬件结构(包括时钟、寄存器、锁存器)进行规则检查

● 包括预装全面的设计规则检查和规范集。

● 针对Synopsys工具性能优化的HDL代码检查,以确保与工具(如Design Compiler、VCS和Formality)的最新功能要求兼容  | | | | | |

|

|

|

| |

|