10101010倍到10 倍的RTLRTLRTLRTL性能

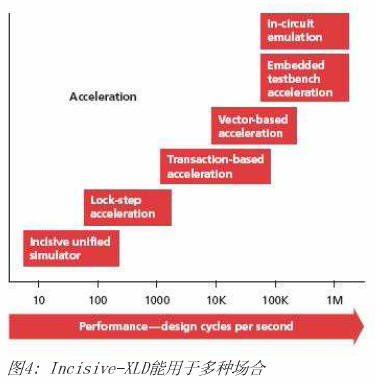

Incisive-XLD 提供按需加速功能,Base设计团队验证系统。它是一个特殊配置的Cadence Paladium加速器/ 仿真器-大量并行布尔计算引擎。与RTL模拟相比的性能增强依赖特定的设计和验证类型。

典型值,加速/仿真模式:

o 10倍到10倍,兼容行为级的测试台使用Paladium信号导向的同步模式

o 10倍到10倍,基于事务的加速 嵌入式测试台或者电路内仿真

最快的模式,,达成终极SOC验证目标-全面的应用级软件测试。

使用模型的进步最大化效率

Incisive-XLD设计团队验证解决了纳米工艺中的关键性能瓶颈。在设计周期早,设计团队可以运用Incisive-XLD模拟行为级的事务级,比RTL 快10 倍。 结果是得到一个功能性虚原型,用于软件开发和作为RTL设的一个可执行定义。随着开始RTL代码设计运时间变长,你团队以用同一个Incisive-XLD产品的硬件加速获得10倍的速度增加。对于最终的应用软件系统验证,设计团队可以切换到电路内仿真模式比模拟加速(典型的20到60KHz)快10 倍,能够在tapeout之前进行全面软件测试。 一体化模拟 Incisive一体化模拟器支持 行为级事务, 寄存器级传递,以及门级抽象。在设计周期早,设计团队可以用Incisive-XLD模拟行为的事务级,比RTL快10倍。当开始代码生成后,块可以在系统环境中模拟交织设计和测试台模型,使用任一语言任何抽象层次协同不会带来额外的性能和集成负担。

Lock-step加速

Lock-step加速能够提供快10倍到10倍的模拟性。可综合的RTL 设计代码移入Incisive-XLD Base 加速器, 行为级的测试台代码和存储模型继续运行在工作站上, 使用Incisive一体化模拟器。在熟悉环境下调试,能让我们查看急速器中的RTL信号。

基于事务的加速

基于事务的加速在工作站和加速器之间使用事务级的通信, 而非比特级信号通信。 这降低了量从而提高总体性能事务器分成可综合的RTL部分,置于加速中, 事务部分置于工作站中。 基事务的验证有额外的优点提升逻辑层次调试到事务层次(读和写)

嵌入式测试台和基于向量的加速

在验证需要无数周期的时候,嵌入式测试台加速提供最大加速性能(典型的20-60KHz)。 一个方法就是用可综合的RTL代码写测试台。另一个方法是移植嵌入式软件目标代码或向量到加速器 存储器向量可能来自模拟,测试, 或者其他。 这对设计将要tapeout 之前测试小变化所需的回归特别有用。

电路内仿真

电路内仿真连接仿真器到系统板, 使用实世界的激励进行完整的硬件/软协同验证。设计团队通过在硅片制造前完全应用软来缩短他们的硅量产时间。更进一步,通过在tapeout之前运行件找到臭虫和性能问题, 确保硅片优化修补,而非使用后期软件补丁延迟量产时间。静态目标是电路内仿真的一个变种,其中仿真器连接到目标系统可以启动和停止时钟。这类似软件调试的范例,运行仿真器一段时间后,在定义条件下停止,检查电路和存储器状态然后重新运行。

一体化的调试环境

Incisive-XLD一体化调试环境能让你在测试台和加速设计中显示任一或全部信号。在过程, 无需为了查看一个关键信号重新编译,者重新运行你还能捕捉追踪数据到文件,然后离线调试为其他用户释放加速容量。

本地或远程访问

Incisive-XLD Base加速器/仿真器的现场放置提供最大的灵活性和最高可获得性,远程访问位于Cadence 设施系统能够提供额外的加速容量。在后一种情况下, 提供完全的安全措施通过特定的ISDN连接或私人VPN。实际上,使用Incisive-XLD Base 远程 访问功能, IC设计团队甚至能够提供室内或者客户系统设计团队远团队的加速或仿真的设计,在硅片远未制造之前。

CADENCE EDAEDAEDAEDA卡带来的最大灵活性

Cadence EDA卡提供了方便的法来随着你的设计团队增大而加大加速器容量方法。项目验证阶段通常有高峰,经常在的最后几个星期那时多个团成员可能需要运行全面的,全芯片加速验证。EDA Card允许以最小的代价满足短期,峰值容量需要。