2.4 I/O并行端口

并行端口即信号各位同时传送的端口。台式PC的并行端口为25位D形接口,应用于打印机的连接。

51单片机有4个8位的并行I/O口,即P0、P1、P2和P3。每个接口都有一个8位数据锁存器和一个8位数据缓冲器,其中,8位数据锁存器属于特殊功能寄存器(SFR),与接口号P0、P1、P2和P3同名,可进行位操作,用于存放需要输出的数据,8个数据缓冲器用于对接口引脚上的数据进行缓冲,但不能锁存,两个三态输入缓冲器分别用于锁存器数据和引脚数据的输入缓冲。另外还包括输出驱动器和逻辑电路等。

锁存就是把信号暂存以维持某种电平状态。锁存器就是用来实现信号锁存功能的器件,输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被传送到输出,直到下一个锁存信号到来时才改变。锁存器的主要作用是缓存,其次是完成高速的控制与其慢速的外设不同步问题,同时解决驱动的问题和一个I/O口既能输出也能输入的问题。

缓冲器是一种用于匹配、隔离两个不同性质电路的逻辑器件,多用在总线上,其作用是提高驱动能力、隔离前后级,缓冲器多半有三态输出功能。通常,三态门作为输出缓冲器,主要用于共享数据总线,为避免多个门同时输出时占用数据总线,使能(EN)信号中只允许有一个为有效电平。

下面对每个口的介绍以位结构进行说明。由于单片机的软硬件是不可分割的整体,所以在以下叙述中会不可避免地涉及软件指令,当提到软件指令时,初学者可以翻看书后的内容,先了解一下相关指令。

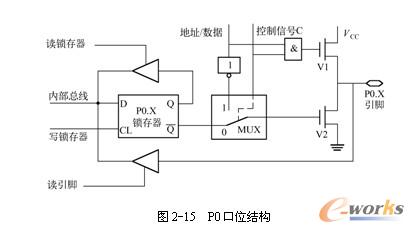

2.4.1 P0口的结构

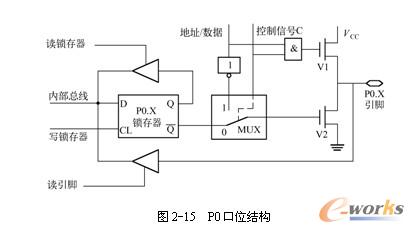

P0口由一个输出锁存器、一个转换开关MUX、两个三态输入缓冲器、输出驱动电路和一个与门及一个反相器组成,如图2-15所示。其中,控制信号C的状态决定转换开关的位置。当C=0时,开关处于图2-14所示位置;当C=1时,开关拨向反相器输出端位置。

1.P0用作通用I/O接口

当系统不进行片外存储器扩展时,P0用做通用I/O口。在这种情况下,单片机硬件自动使MUX开关接向锁存器的反相输出端。另外,与门输出的“0”使输出驱动器的上拉场效应晶体管V1处于截止状态。因此,输出驱动级工作在需外接上拉电阻的漏极开路方式。

作输出口时,微处理器执行口的输出指令,内部数据总线上的数据在“写锁存器”信号的作用下由D端进入锁存器,经锁存器的反向端送至场效应晶体管V2,再经V2反向,在P0.X引脚出现的数据正好是内部总线的数据。

作输入口时,数据可以读口的锁存器,也可以读口的引脚。这要根据输入操作采用的是“读锁存器”指令还是“读引脚”指令来决定。

执行“读-修改-写”类输入指令时(如ANL P0,A),内部产生的“读锁存器”操作信号使锁存器Q端数据进入内部数据总线,在与累加器A进行逻辑运算之后,结果又送回P0的口锁存器,并出现在引脚。读口锁存器可以避免因外部电路原因使原口引脚的状态发生变化而造成误读。

在执行“MOV”类输入指令时(如MOV A,P0),内部产生的操作信号是“读引脚”。注意,在执行该类输入指令前要先把锁存器写入“1”,使场效应晶体管V2截止,使引脚处于悬浮状态,可以作为高阻抗输入。否则,在作为输入方式之前曾向锁存器输出过“0”,则V2导通会使引脚钳位在“0”电平,使输入高电平“1”无法读入。所以,P0口在作为通用I/O口时,属于双向口。双向口指的是P0口内部无上拉电阻,除高、低电平状态外,还存在高阻状态。

2.P0用作地址/数据总线

当系统进行片外ROM扩展(此时

)或进行片外RAM扩展(外部RAM传送使用“MOVX @DPTR”或“MOVX @Ri”类指令)时,P0用作地址/数据总线。在这种情况下,单片机内的硬件自动使MUX开关拨向反相器的输出端,这时与门的输出由地址/数据线的状态决定。

微处理器在执行输出指令时,低8位地址信息和数据信息分时地出现在地址/数据总线上。若地址/数据线的状态为“1”,则场效应晶体管V1导通、V2截止,引脚状态为“1”;若地址/数据线的状态为“0”,则场效应晶体管V1截止、V2导通,引脚状态为“0”。P0.X引脚的状态与地址/数据线的信息相同。低8位地址由ALE信号的负跳变使它锁存到外部地址锁存器中。

微处理器在执行输入指令时,首先低8位地址信息出现在地址/数据总线上,P0.X引脚的状态与地址/数据总线的地址信息相同。然后,微处理器自动地使转换开关MUX拨向锁存器,并向P0口写入FFH,同时“读引脚”信号有效,数据经缓冲器进入内部数据总线。

P0口作为地址/数据总线使用时,也是一个双向口。

2.4.2 P1口的结构

P1口由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成,驱动电路内部设有上拉电阻,如图2-16所示。

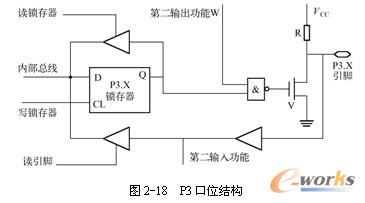

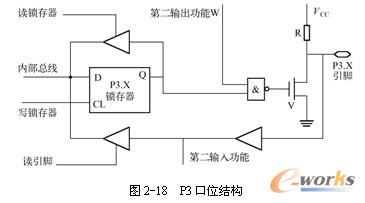

1.P3用做第一功能的通用I/O口

对P3口进行字节或位寻址时,单片机内部的硬件自动将第二功能输出线W置1。这时,对应的口线为通用I/O口方式。

输出时,锁存器的状态(Q端)与输出引脚的状态相同;输入时,首先要向口锁存器写入1,使引脚处于高阻输入状态。输入的数据在“读引脚”信号的作用下,进入内部数据总线。

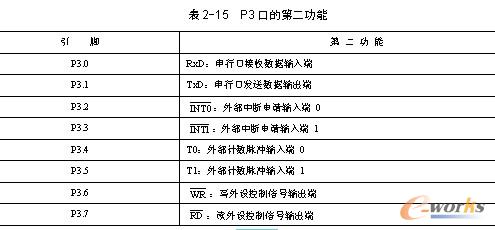

2.P3用做第二功能使用

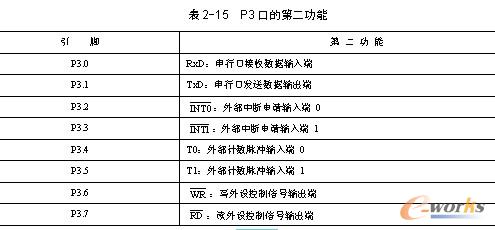

当微处理器不对P3口进行字节或位寻址时,内部硬件自动将口锁存器的Q端置1。这时,P3口作为第二功能使用,见表2-15。

作为输出功能的口线(如TxD等),由于该位的锁存器已自动置1,“与非”门对第二功能输出是畅通的,即引脚的状态与第二功能输出是相同的。

作为输入功能的口线(如RxD等),由于此时该位的锁存器和第二功能输出线均为1,场效应晶体管V截止。引脚信号经输入缓冲器(非三态门)进入单片机内部的第二功能输入线。

2.4.5 并行端口的负载能力

51单片机的P0口输出缓冲器能驱动8个低功耗肖特基TTL(Lower-power schottky TTL,LSTTL)电路,驱动MOS电路须外接上拉电阻,但P0口用作地址/数据总线时,可直接驱动MOS的输入而不必外接上拉电阻。

P1、P2和P3口的输出缓冲器可驱动4个LSTTL电路。HMOS及CHMOS型单片机的I/O口由集电极开路或漏极开路的输出来驱动,不必外加上拉电阻。

51单片机的I/O口上通常接有电阻(作用是把电压上拉到5V),这里主要是为了提高输出驱动能力的。因为8051的I/O口不是标准的I/O口,输出为低电平时可以吸收20mA的电流,但输出为高电平时是通过内部一个很大的电阻上拉的,输出高电平时驱动能力很差,所以就通过外部上拉来提高电平输出驱动能力。

)或进行片外RAM扩展(外部RAM传送使用“MOVX @DPTR”或“MOVX @Ri”类指令)时,P0用作地址/数据总线。在这种情况下,单片机内的硬件自动使MUX开关拨向反相器的输出端,这时与门的输出由地址/数据线的状态决定。

)或进行片外RAM扩展(外部RAM传送使用“MOVX @DPTR”或“MOVX @Ri”类指令)时,P0用作地址/数据总线。在这种情况下,单片机内的硬件自动使MUX开关拨向反相器的输出端,这时与门的输出由地址/数据线的状态决定。