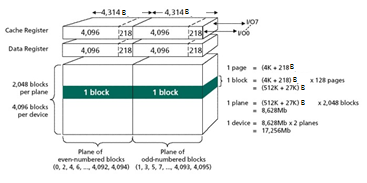

图3-35 Flash芯片逻辑图

如图3-36所示为Intel X-25M固态硬盘的拆机图,可以看到它使用了10片NAND Flash芯片,左上方为SSD控制器,左下方为RAM Buffer。最左侧为SATA物理接口。

图3-36 Cell阵列有序排布图

如图3-37所示为某SSD控制器芯片的方框图。其中包含多个逻辑模块,外围接口部分和底层供电部分我们就不去关心了。这里将目光集中在右半边,其中8051CPU通过将ROM中的Firmware载入IRAM中执行来实现SSD的数据IO和管理功能。Flash Controller负责向所有连接的NAND Flash芯片执行读写任务,每个NAND芯片用8b并行总线与Flash Controller上的每个通道连接,每时钟周期并行传递8b数据。Flash Controller与Flash芯片之间也是通过指令的方式来运作的,地址信息与数据信息都在这8位总线上传送,由于总线位宽太窄,所以一个简单的寻址操作就需要多个时钟周期才能传送完毕。芯片容量越大,那么地址也就越长,寻址时间也就越长,所以,对于小块随机IO,Flash会随着容量的增加而变得越来越低效。新的Flash芯片已经

ICP经营许可证:鄂B2-20080078

(于2003年首获许可证:鄂B2-20030029)

鄂公网安备:420100003343号

© 2002-2025 武汉制信科技有限公司 版权所有

投诉举报电话:027-87592219